# **ModelSim® SE Reference Manual**

Software Version 6.6a

© 1991-2010 Mentor Graphics Corporation All rights reserved.

This document contains information that is proprietary to Mentor Graphics Corporation. The original recipient of this document may duplicate this document in whole or in part for internal business purposes only, provided that this entire notice appears in all copies. In duplicating any part of this document, the recipient agrees to make every reasonable effort to prevent the unauthorized use and distribution of the proprietary information.

This document is for information and instruction purposes. Mentor Graphics reserves the right to make changes in specifications and other information contained in this publication without prior notice, and the reader should, in all cases, consult Mentor Graphics to determine whether any changes have been made.

The terms and conditions governing the sale and licensing of Mentor Graphics products are set forth in written agreements between Mentor Graphics and its customers. No representation or other affirmation of fact contained in this publication shall be deemed to be a warranty or give rise to any liability of Mentor Graphics whatsoever.

MENTOR GRAPHICS MAKES NO WARRANTY OF ANY KIND WITH REGARD TO THIS MATERIAL INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE.

MENTOR GRAPHICS SHALL NOT BE LIABLE FOR ANY INCIDENTAL, INDIRECT, SPECIAL, OR CONSEQUENTIAL DAMAGES WHATSOEVER (INCLUDING BUT NOT LIMITED TO LOST PROFITS) ARISING OUT OF OR RELATED TO THIS PUBLICATION OR THE INFORMATION CONTAINED IN IT, EVEN IF MENTOR GRAPHICS CORPORATION HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

#### **RESTRICTED RIGHTS LEGEND 03/97**

U.S. Government Restricted Rights. The SOFTWARE and documentation have been developed entirely at private expense and are commercial computer software provided with restricted rights. Use, duplication or disclosure by the U.S. Government or a U.S. Government subcontractor is subject to the restrictions set forth in the license agreement provided with the software pursuant to DFARS 227.7202-3(a) or as set forth in subparagraph (c)(1) and (2) of the Commercial Computer Software - Restricted Rights clause at FAR 52.227-19, as applicable.

#### Contractor/manufacturer is:

Mentor Graphics Corporation 8005 S.W. Boeckman Road, Wilsonville, Oregon 97070-7777. Telephone: 503.685.7000 Toll-Free Telephone: 800.592.2210 Website: www.mentor.com SupportNet: supportnet.mentor.com/ Send Feedback on Documentation: supportnet.mentor.com/user/feedback\_form.cfm

**TRADEMARKS**: The trademarks, logos and service marks ("Marks") used herein are the property of Mentor Graphics Corporation or other third parties. No one is permitted to use these Marks without the prior written consent of Mentor Graphics or the respective third-party owner. The use herein of a third-party Mark is not an attempt to indicate Mentor Graphics as a source of a product, but is intended to indicate a product from, or associated with, a particular third party. A current list of Mentor Graphics' trademarks may be viewed at: www.mentor.com/terms\_conditions/trademarks.cfm.

# **Table of Contents**

| Chapter 1                                                |              |

|----------------------------------------------------------|--------------|

| Syntax and Conventions                                   | 15           |

| Documentation Conventions                                | 15           |

| File and Directory Pathnames                             | 16           |

| Design Object Names                                      | 16           |

| Object Name Syntax                                       | 16           |

| SystemC Class, Structure, and Union Member Specification | 17           |

| SystemVerilog Scope Resolution Operator                  | 18           |

| Specifying Names                                         | 19           |

| Escaping Brackets and Spaces in Array Slices             | 21           |

| Environment Variables and Pathnames                      | 21           |

| Name Case Sensitivity                                    | 21           |

| Extended Identifiers                                     | 22           |

| Wildcard Characters.                                     | 22           |

| Using the WildcardFilter Preference Variable             | 23           |

| Simulator Variables                                      | 28           |

| Simulation Time Units                                    | 28           |

| Argument Files.                                          | 29           |

| Command Shortcuts                                        | 30           |

| Command History Shortcuts                                | 30           |

| Numbering Conventions                                    | 31           |

| VHDL Numbering Conventions                               | 31           |

| Verilog Numbering Conventions                            | 32           |

| GUI_expression_format.                                   | 32           |

| Expression Typing                                        | 33           |

| Expression Syntax.                                       | 33           |

| Signal and Subelement Naming Conventions.                | 39           |

| Grouping and Precedence                                  | 39           |

| Concatenation of Signals or Subelements.                 | 39           |

| Record Field Members                                     | 41           |

| Searching for Binary Signal Values in the GUI            | 41           |

| Chapter 2                                                |              |

| Commands                                                 | 43           |

|                                                          | 57           |

| .main clear                                              | 57           |

| abort                                                    | - 30<br>- 59 |

| add atv                                                  | 59<br>60     |

| add button                                               | 63           |

| add dataflowadd list                                     | 65           |

| add fistadd memory                                       | - 03<br>- 70 |

| add memory                                               | 70           |

|                                                          | 14           |

| add testbrowser  | 74 |

|------------------|----|

| add watch        | 75 |

| add wave         | 76 |

| add_cmdhelp      | 83 |

| add_menu         | 85 |

| add_menucb       | 87 |

| add_menuitem     | 89 |

| add_separator    | 91 |

| add_submenu      | 92 |

| alias            | 94 |

| assertion action | 95 |

| assertion active | 97 |

| assertion count  | 99 |

| assertion enable | 01 |

|                  | 04 |

|                  | 06 |

|                  | 08 |

|                  | 10 |

|                  | 12 |

|                  | 13 |

|                  | 15 |

|                  | 17 |

|                  | 18 |

|                  | 19 |

|                  | 20 |

| 1                | 27 |

|                  | 28 |

|                  | 31 |

|                  | 34 |

|                  | 35 |

|                  | 37 |

|                  | 38 |

|                  | 39 |

|                  | 41 |

|                  | 42 |

|                  | 43 |

|                  | 44 |

|                  | 46 |

| compare add 1    | 48 |

| 1                | 54 |

|                  | 56 |

|                  | 58 |

|                  | 60 |

|                  | 61 |

| compare end 1    | 62 |

|                  | 63 |

|                  | 65 |

|                  | 66 |

|                  | 71 |

| compare reset      | 172 |

|--------------------|-----|

| compare run        | 173 |

| compare savediffs  | 174 |

| compare saverules  | 175 |

| compare see.       | 176 |

| compare start      | 178 |

| compare stop       | 180 |

| compare update     | 181 |

| configure          | 182 |

| context.           | 188 |

| coverage analyze   | 191 |

| coverage attribute | 198 |

| coverage clear     | 201 |

| coverage edit      | 203 |

| coverage exclude   | 205 |

| coverage goal      | 212 |

| coverage open      | 215 |

| coverage ranktest  | 216 |

| coverage report    | 221 |

| coverage save      | 232 |

| coverage tag       | 234 |

| coverage testnames | 238 |

| coverage unlinked  | 239 |

| coverage weight    | 242 |

| dataset alias      | 245 |

| dataset clear      | 246 |

| dataset close      | 247 |

| dataset config     | 248 |

| dataset current    | 250 |

| dataset info       | 251 |

| dataset list       | 252 |

| dataset open       | 253 |

| dataset rename.    | 254 |

| dataset restart    | 255 |

| dataset save       | 256 |

| dataset snapshot   | 257 |

| delete             | 260 |

| describe           | 261 |

| disablebp          | 262 |

| disable_menu       | 263 |

| disable_menuitem   | 264 |

| do                 | 265 |

| down               | 267 |

| drivers            | 270 |

| dumplog64          | 271 |

| echo               | 272 |

| edit.              | 273 |

| enablebp           | 274 |

| enable_menu        | 275 |

| enable_menuitem       | 276 |

|-----------------------|-----|

| encoding              | 277 |

| environment           | 278 |

| examine               | 280 |

| exit                  | 285 |

| fcover configure      | 286 |

| find                  | 289 |

| find drivers          | 294 |

| find infiles          | 299 |

| find insource         | 300 |

| formatTime            | 302 |

| force                 | 303 |

| fsm list              | 307 |

| fsm properties        | 308 |

| fsm view              | 309 |

| gdb dir               | 310 |

| getactivecursortime   | 311 |

| getactivemarkertime   | 312 |

| help                  | 313 |

| history               | 314 |

| jobspy                | 315 |

| layout.               | 316 |

| lecho                 | 318 |

| left                  | 319 |

| log                   | 322 |

| lshift                | 326 |

| lsublist.             | 327 |

| mem compare           | 328 |

| mem display           | 329 |

| mem list.             | 332 |

| mem load.             | 333 |

| mem save              | 337 |

| mem search            | 340 |

| messages clearfilter. | 343 |

| messages setfilter    | 344 |

| modelsim.             | 345 |

| next                  | 346 |

| noforce               | 347 |

| nolog                 | 348 |

| notepad               | 350 |

| noview.               | 351 |

| nowhen                | 352 |

| onbreak               | 353 |

| onElabError.          | 355 |

| onerror.              | 356 |

| onfinish              | 358 |

|                       | 359 |

| pa msg                | 361 |

|                       | 362 |

| pop                   | 302 |

| power add         | 363 |

|-------------------|-----|

| power off         | 365 |

| power on          | 367 |

| power report      | 369 |

| power reset       | 372 |

| precision         | 374 |

| printenv          | 375 |

| process report    | 376 |

| profile clear     | 377 |

| profile interval. | 378 |

| profile off       | 379 |

| profile on        | 380 |

| profile open      | 382 |

| profile option.   | 383 |

| profile reload    | 385 |

| profile report    | 386 |

| profile save      | 390 |

| project           | 391 |

| property list     | 394 |

| property wave     | 396 |

| push              | 398 |

| pwd               | 399 |

|                   | 400 |

| quit              | 401 |

| qverilog          | 402 |

| radix             | 404 |

| radix define      | 406 |

| radix delete      | 409 |

|                   | 410 |

| radix names       | 411 |

| radix signal      | 412 |

| readers           | 413 |

| report            | 414 |

| 1                 | 416 |

| restore           | 418 |

| resume            | 419 |

| right             | 420 |

| run               | 423 |

| runStatus         | 426 |

| sccom             | 428 |

| scgenmod          | 436 |

| sdfcom.           | 439 |

| search            | 441 |

| searchlog         | 444 |

| see               | 447 |

| seetime           | 448 |

| setenv            | 450 |

| shift             | 451 |

| show              | 452 |

| simstats                               | 453 |

|----------------------------------------|-----|

| status                                 | 455 |

| step                                   | 456 |

| stop                                   | 457 |

| suppress                               | 458 |

| tb                                     | 459 |

| tcheck_set                             | 460 |

| tcheck_status                          | 464 |

| Time                                   | 467 |

| toggle add                             | 470 |

| toggle disable                         | 473 |

| toggle enable                          | 474 |

| toggle report                          | 475 |

| toggle reset                           | 477 |

| tr color                               | 478 |

| tr order                               | 481 |

| tr uid                                 | 483 |

| transcribe                             | 485 |

| transcript                             | 486 |

| transcript file                        | 487 |

| transcript path                        | 489 |

| transcript sizelimit.                  | 490 |

| tssi2mti                               | 491 |

| typespec.                              | 492 |

| ui_VVMode                              | 493 |

| unsetenv                               | 495 |

| up                                     | 496 |

| vcd add                                | 498 |

| vcd checkpoint                         | 500 |

| vcd comment                            | 501 |

| vcd dumpports                          | 502 |

| vcd dumpportsall.                      | 505 |

| vcd dumpportsflush                     | 506 |

| vcd dumpportslimit                     | 507 |

| vcd dumpportsoff                       | 508 |

| vcd dumpportson.                       | 509 |

| vcd file                               | 510 |

| vcd files.                             | 512 |

| vcd flush                              | 514 |

| vcd limit                              | 515 |

| vcd off                                | 516 |

| vcd on                                 | 517 |

| vcd2wlf                                | 518 |

| vcom                                   | 520 |

| vcover attribute                       | 538 |

| vcover dump                            | 540 |

| vcover merge.                          | 542 |

| vcover merge                           | 548 |

| vcover report                          | 554 |

| ······································ | r   |

| vcover stats       | 565 |

|--------------------|-----|

| vcover testnames   | 568 |

| vdbg               | 570 |

| vdel               | 571 |

| vdir               | 573 |

| vencrypt           | 576 |

| verror             | 578 |

| vgencomp           | 580 |

| vhencrypt          | 582 |

| view               | 584 |

| virtual count      | 588 |

| virtual define     | 589 |

| virtual delete     | 590 |

| virtual describe   | 591 |

| virtual expand     | 592 |

| virtual function   | 593 |

| virtual hide       | 596 |

| virtual log        | 597 |

| virtual nohide     | 599 |

| virtual nolog      | 600 |

| virtual region     | 602 |

| virtual save       | 603 |

| virtual show       | 604 |

| virtual signal     | 605 |

| virtual type       | 609 |

| vlib               | 611 |

| vlog               | 613 |

| vmake              | 639 |

| vmap               | 641 |

| vopt               | 642 |

| vsim               | 676 |

| vsim <info></info> | 715 |

| vsim_break         | 716 |

| vsource            | 717 |

| wave               | 718 |

| wave create        | 722 |

| wave edit          | 728 |

| wave export        | 731 |

| wave import        | 732 |

| wave modify        | 733 |

| wave sort.         | 736 |

| when               | 737 |

| where              | 744 |

| wlf2log            | 745 |

| wlf2vcd            | 748 |

| wlfman             | 749 |

| wlfrecover         | 753 |

| write cell_report  | 754 |

| write format.      | 755 |

| write list                                      | 757        |

|-------------------------------------------------|------------|

| write preferences                               | 758        |

| write report                                    | 759        |

| write timing                                    | 762        |

| write transcript                                | 763        |

| write tssi                                      | 764        |

| write wave                                      | 766        |

| xml2ucdb                                        | 768        |

| Chapter 3                                       |            |

| AVM Encyclopedia                                | 773        |

| Class Index                                     | 773        |

| Classes for Components.                         | 778        |

| avm_env                                         | 779        |

| avm_named_component                             | 781        |

| avm_nancd_component                             | 786        |

| avm_stimulus                                    | 788        |

| avm_subscriber                                  | 789        |

| avm_threaded_component                          | 790        |

| avm_uncaded_componentavm_verification_component | 791        |

| Classes for Comparators                         | 791        |

| avm_algorithmic_comparator.                     | 793        |

| avm_in_order_built_in_comparator                | 795        |

| avm_in_order_class_comparator                   | 796        |

| avm_in_order_comparator                         | 797        |

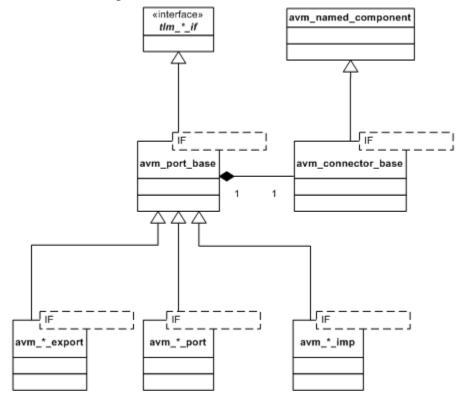

| Classes for Connectors.                         | 799        |

| avm_*_export                                    | 800        |

| avmcxport                                       | 800        |

| avm_*_port                                      | 802        |

| avm_analysis_port                               | 804        |

| avm_blocking_master_imp                         | 800        |

| avm_blocking_slave_imp                          | 807        |

| avm_blocknig_slave_nnpavm_connector_base        | 811        |

|                                                 | 815        |

| avm_master_impavm_nonblocking_master_imp        | 817        |

| avm_nonblocking_slave_imp                       | 819        |

| <b>U</b>                                        | 819        |

| avm_port_base                                   | 823        |

| avm_slave_imp                                   | 825<br>825 |

| avm_transport_imp                               | 825        |

| analysis_imp                                    | 820        |

| analysis_port                                   | 827        |

| global_analysis_ports                           | 829        |

| tlm_*_imp                                       |            |

| Classes for Channels                            | 829<br>821 |

| analysis_fifo                                   | 831<br>832 |

| tlm_fifo                                        | 832<br>835 |

| tlm_req_rsp_channeltlm_transport_channel        |            |

|                                                 | 030        |

| TLM Interfaces              | 838 |

|-----------------------------|-----|

| analysis_if #(type T=int)   | 839 |

| tlm_blocking_get_if         | 840 |

| tlm_blocking_get_peek_if    | 841 |

| tlm_blocking_peek_if        | 842 |

| tlm_blocking_put_if         | 843 |

| tlm_blocking_master_if      | 844 |

| tlm_blocking_slave_if       | 845 |

| tlm_get_if                  | 846 |

| tlm_get_peek_if             | 847 |

| tlm_master_if               | 849 |

| tlm_nonblocking_get_if      |     |

| tlm_nonblocking_get_peek_if | 852 |

| tlm_nonblocking_master_if   | 853 |

| tlm_nonblocking_peek_if     | 855 |

| tlm_nonblocking_put_if      | 856 |

| tlm_nonblocking_slave_if    | 857 |

| tlm_peek_if                 | 859 |

| tlm_put_if                  | 860 |

| tlm_slave_if                | 861 |

| tlm_transport_if            | 863 |

| Transactions                | 863 |

| avm_built_in_clone          | 864 |

| avm_built_in_comp           | 865 |

| avm_built_in_converter      | 866 |

| avm_built_in_pair           | 867 |

| avm_class_clone             | 868 |

| avm_class_comp              | 869 |

| avm_class_converter         | 870 |

| avm_class_pair              | 871 |

| avm_transaction             | 872 |

| Reporting                   | 873 |

| avm_report_client           | 874 |

| avm_report_handler          | 879 |

| avm_report_server           | 882 |

| avm_reporter                | 884 |

|                             |     |

#### Index

**End-User License Agreement**

# **List of Examples**

| Example 1-1. Base- and Descendant-Class Specification        | 17 |

|--------------------------------------------------------------|----|

| Example 1-2. SystemVerilog Scope Resolution Operator Example | 19 |

# **List of Figures**

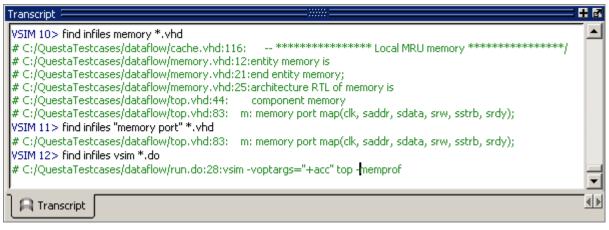

| Figure 2-1. find infiles Example               | 299 |

|------------------------------------------------|-----|

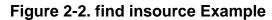

| Figure 2-2. find insource Example.             | 301 |

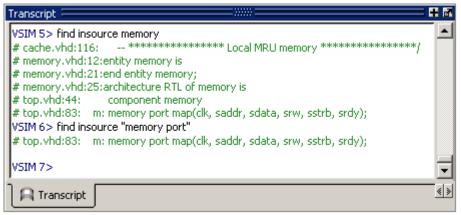

| Figure 3-1. UML Diagram for Components         | 778 |

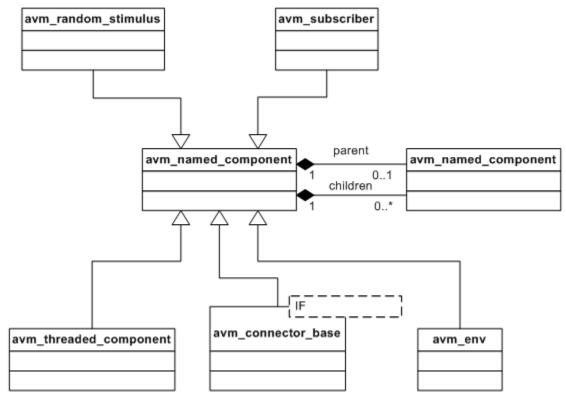

| Figure 3-2. UML Diagram for Comparator Classes | 792 |

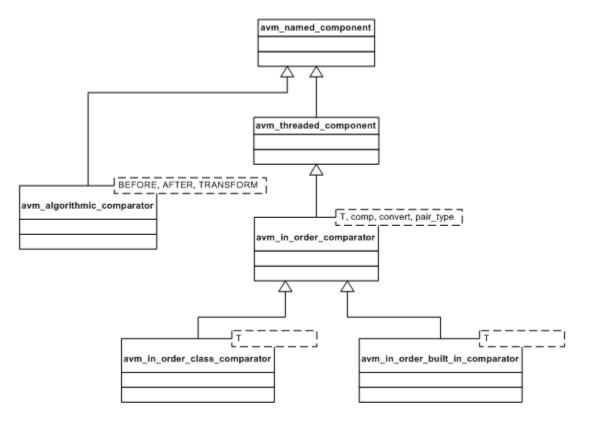

| Figure 3-3. UML Diagram for Connectors         | 799 |

| Figure 3-4. UML Diagram for Channels           | 830 |

| Figure 3-5. UML Diagram for Reporting Classes  | 873 |

# **List of Tables**

| Table 1-1. Conventions for Command Syntax                     | 15  |

|---------------------------------------------------------------|-----|

| Table 1-2. Examples of Object Names                           | 20  |

| Table 1-3. Wildcard Characters in HDL Object Names            | 23  |

| Table 1-4. WildcardFilter Arguments                           | 24  |

| Table 1-5. WildcardFilter Argument Groups                     | 26  |

| Table 1-6. Keyboard Shortcuts for Command History             | 30  |

| Table 1-7. VHDL Number Conventions: Style 1                   | 31  |

| Table 1-8. VHDL Number Conventions: Style 2                   | 31  |

| Table 1-9. Verilog Number Conventions                         | 32  |

| Table 1-10. Constants Supported for GUI Expressions           | 35  |

| Table 1-11. Array Constants Supported for GUI Expressions     | 35  |

| Table 1-12. Variables Supported for GUI Expressions           | 35  |

| Table 1-13. Array Variables Supported for GUI Expressions     | 36  |

| Table 1-14. Operators Supported for GUI Expressions           | 37  |

| Table 1-15. Casting Conversions Supported for GUI Expressions | 38  |

| Table 1-16. VHDL Logic Values Used in GUI Search              | 42  |

| Table 1-17. Verilog Logic Values Used in GUI Search           | 42  |

| Table 2-1. Supported Commands                                 | 43  |

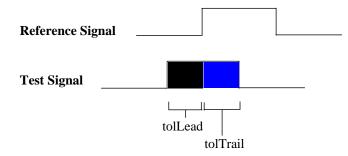

| Table 2-2. Comparing Reference Objects to Test Objects        | 148 |

| Table 2-3. Order and Type of Ranked Tests                     | 216 |

| Table 2-4. runStatus Command States                           | 426 |

| Table 2-5. runStatus -full Command Information                | 426 |

| Table 2-6. Field Arguments for Window Searches                | 442 |

| Table 2-7. Output Fields for tcheck_status Command            | 465 |

| Table 2-8. Warning Message Categories for vcom -nowarn        | 532 |

| Table 2-9. Order and Type of Ranked Tests                     | 548 |

| Table 2-10. Design Unit Properties                            | 574 |

| Table 2-11. Warning Message Categories for vlog -nowarn       | 631 |

| Table 2-12. Warning Message Categories for vopt -nowarn       | 660 |

| Table 2-13. Wave Window Commands for Cursor                   | 718 |

| Table 2-14. Wave Window Commands for Expanded Time Display    | 718 |

| Table 2-15. Wave Window Commands for Controlling Display      | 719 |

| Table 2-16. Wave Window Commands for Zooming                  | 719 |

| Table 3-1. Class Index                                        | 773 |

| Table 3-2. Exports and Interfaces                             | 800 |

| Table 3-3. Interface Implementations                          | 803 |

| Table 3-4. Ports and Interfaces                               | 804 |

| Table 3-5. Deprecated Implementations                         | 829 |

# **Documentation Conventions**

This manual uses the following conventions to define ModelSim<sup>™</sup> command syntax.

| Syntax notation | Description                                                                                                                                                                                                                                 |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| < >             | angled brackets surrounding a syntax item indicate a<br>user-defined argument; do not enter the brackets in<br>commands                                                                                                                     |

| []              | square brackets generally indicate an optional item; if<br>the brackets surround several words, all must be<br>entered as a group; the brackets are not entered <sup>1</sup>                                                                |

| { }             | braces indicate that the enclosed expression contains<br>one or more spaces yet should be treated as a single<br>argument, or that the expression contains square<br>brackets for an index; for either situation, the braces<br>are entered |

|                 | an ellipsis indicates items that may appear more than<br>once; the ellipsis itself does not appear in commands                                                                                                                              |

|                 | the vertical bar indicates a choice between items on<br>either side of it; do not include the bar in the command                                                                                                                            |

| monospaced type | monospaced type is used in command examples                                                                                                                                                                                                 |

| #               | comments included with commands are preceded by<br>the number sign (#); useful for adding comments to<br>DO files (macros)                                                                                                                  |

Table 1-1. Conventions for Command Syntax

1. One exception to this rule is when you are using Verilog syntax to designate an array slice. For example,

add wave {vector1[4:0]}

The square brackets in this case denote an index. The braces prevent the Tcl interpreter from treating the text within the square brackets as a Tcl command.

#### Note \_

Neither the prompt at the beginning of a line nor the <Enter> key that ends a line is shown in the command examples.

# **File and Directory Pathnames**

Several ModelSim commands have arguments that point to files or directories. For example, the **-y** argument to vlog specifies the Verilog source library directory to search for undefined modules. Spaces in file pathnames must be escaped or the entire path must be enclosed in quotes. For example:

#### vlog top.v -y C:/Documents\ and\ Settings/projects/dut

or

vlog top.v -y "C:/Documents and Settings/projects/dut"

# **Design Object Names**

Design objects are organized hierarchically. Each of the following objects creates a new level in the hierarchy:

- VHDL component instantiation statement, block statement, and package

- Verilog module instantiation, named fork, named begin, task and function

- SystemVerilog class, package, program, and interface

- **SystemC** module instantiation

### **Object Name Syntax**

The syntax for specifying object names in ModelSim is as follows:

```

[<dataset_name><datasetSeparator>][<pathSeparator>][<hierarchicalPath>]

<objectName>[<elementSelection>]

```

where

- **dataset\_name** is the name mapped to the WLF file in which the object exists. The currently active simulation is the "sim" dataset. Any loaded WLF file is referred to by the logical name specified when the WLF file was loaded. Refer to the chapter "Recording Simulation Results With Datasets" in the User's Manual for more information.

- **datasetSeparator** is the character used to terminate the dataset name. The default is colon (:), though a different character (other than backslash (\)) may be specified as the dataset separator via the DatasetSeparator variable in the *modelsim.ini* file. The default is a colon (:). This character must be different than the pathSeparator character.

- **pathSeparator** is the character used to separate hierarchical object names. Normally, a backslash ( / ) is used for VHDL and a period ( . ) is used for Verilog, although other characters (except a backslash ( \ )) may be specified via the PathSeparator variable in

the *modelsim.ini* file. This character must be different than the datasetSeparator. Both (.) and forward slash (/) can be used for SystemC. Neither (.) nor (/) can be used when referring to the contents of a SystemVerilog package or class.

- **hierarchicalPath** is a set of hierarchical instance names separated by a path separator and ending in a path separator prior to the objectName. For example, */top/proc/clk*.

- **objectName** is the name of an object in a design.

- **elementSelection** indicates some combination of the following:

- **Array indexing** Single array elements are specified using either parentheses "()" or square brackets "[]" around a single number.

- Array slicing Slices (or part-selects) of arrays are specified using either parentheses (()) or square brackets ([]) around a range specification. A range is two numbers separated by one of the following: " to ", " downto ", or a colon (:). See Escaping Brackets and Spaces in Array Slices for important information about using square brackets in ModelSim commands.

- **Record field selection** A record field is specified using a period ( . ) followed by the name of the field.

- C++ class, structure, and union member selection A class, structure, or union member is specified using the record field specification syntax, described just above.

# SystemC Class, Structure, and Union Member Specification

You can specify members of SystemC structures and classes using HDL record syntax. The syntax for specifying members of a base class using ModelSim is different than C++. In C++, it is not necessary to specify the base class:

<instance>.<base\_member>

Whereas, in ModelSim you *must* include the name of the base class:

<instance>.<base>.<base\_member>

#### Example 1-1. Base- and Descendant-Class Specification

Let's say you have a base class and a descendant class:

```

class dog

{

private:

int value;

};

```

```

class beagle : public dog

{

private:

int value;

dog d;

};

```

You have an sc\_signal<> of type beagle somewhere in your code:

```

sc_signal<beagle> spot;

```

Legal names for viewing this signal are:

```

spot

spot.*

spot.value

spot.dog

spot.dog.*

spot.dog.value

```

Now, to examine the member *value* of the base class *dog*, you would type:

exa spot.dog.value

To examine the member *value* of member *d*, you would type:

exa spot.d.value

To examine the member *value*, you would type:

exa spot.value

# SystemVerilog Scope Resolution Operator

SystemVerilog offers the scope resolution operator, double colon (::), for accessing classes within a package and static data within a class. The example below shows various methods of using this operator as well as alternatives using standard hierarchical references.

#### Example 1-2. SystemVerilog Scope Resolution Operator Example

```

package myPackage;

class packet;

static int a[0:1] = {1, 2};

int b[0:1];

int c;

function new;

b[0] = 3;

b[1] = 4;

c = a[0];

endfunction

endclass

endpackage : myPackage

module top;

myPackage::packet my = new;

int myint = my.a[1];

endmodule

```

The following examine examples access data from the class packet.

```

examine myPackage::packet::a

examine /top/my.a

```

Both of the above commands return the contents of the static array *a* within class *packet*.

```

examine myPackage::packet::a(0)

examine /top/my.a(0)

```

Both of the above commands return the contents of the first element of the static array *a* within class *packet*.

```

examine /top/my.b

```

Return the contents of the instance-specific array b.

```

examine /top/my.b(0)

```

Return the contents of the first element of the instance-specific array b.

When referring to the contents of a package or class, you cannot use the standard path separators, a period ( . ) or a forward slash ( / ).

### **Specifying Names**

We distinguish between four "types" of object names: simple, relative, fully-rooted, and absolute.

• **Simple name** — does not contain any hierarchy. It is simply the name of an object (e.g., *clk* or *data[3:0]*) in the current context.

- **Relative name** does not start with a path separator and may or may not include a dataset name or a hierarchical path (e.g., *u1/data* or *view:clk*). A relative name is relative to the current context in the current or specified dataset.

- **Fully-rooted name** starts with a path separator and includes a hierarchical path to an object (e.g., */top/u1/clk*). There is a special case of a fully-rooted name where the top-level design unit name can be unspecified (e.g., */u1/clk*). In this case, the first top-level instance in the design is assumed.

- **Absolute name** is an exactly specified hierarchical name containing a dataset name and a fully rooted name (e.g., *sim:/top/u1/clk*).

The current dataset is used when accessing objects where a dataset name is not specified as part of the name. The current dataset is determined by the dataset currently selected in the Structure window or by the last dataset specified in an environment.

The current context in the current or specified dataset is used when accessing objects with relative or simple names. The current context is either the current process, if any, or the current instance if there is no current process or the current process is not in the current instance. The situation of the current process not being in the current instance can occur, for example, by selecting a different instance in the Structure tab or by using the environment to set the current context to a different instance.

| Table 1-2. Examples of Object Names |                                                                                                                                         |  |

|-------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|--|

| Object Name                         | Description                                                                                                                             |  |

| clk                                 | specifies the object <i>clk</i> in the current context                                                                                  |  |

| /top/clk                            | specifies the object <i>clk</i> in the top-level design unit.                                                                           |  |

| /top/block1/u2/clk                  | specifies the object <i>clk</i> , two levels down from the top-level design unit                                                        |  |

| block1/u2/clk                       | specifies the object <i>clk</i> , two levels down from the current context                                                              |  |

| array_sig[4]                        | specifies an index of an array object                                                                                                   |  |

| {array_sig(1 to 10)}                | specifies a slice of an array object in VHDL or SystemC;<br>see Escaping Brackets and Spaces in Array Slices for more<br>information    |  |

| {mysignal[31:0]}                    | specifies a slice of an array object in Verilog or SystemC;<br>see Escaping Brackets and Spaces in Array Slices for more<br>information |  |

| record_sig.field                    | specifies a field of a record, a C++ class or structure<br>member, or a C++ base class                                                  |  |

Table 1-2 contains examples of various ways of specifying object names.

Table 1-2. Examples of Object Names

### **Escaping Brackets and Spaces in Array Slices**

Because ModelSim is a Tcl-based tool, you must use curly braces ( { } ) to "escape" square brackets and spaces when specifying array slices. For example:

```

toggle add {data[3:0]}

toggle add {data(3 to 0)}

```

For complete details on Tcl syntax, refer to Tcl Command Syntax.

### **Further Details**

As a Tcl-based tool, ModelSim commands follow Tcl syntax. One problem people encounter with ModelSim commands is the use of square brackets ([]) or spaces when specifying array slices. As shown on the previous page, square brackets are used to specify slices of arrays (e.g., *data[3:0]*). However, in Tcl, square brackets signify command substitution. Consider the following example:

set aluinputs [find -in alu/\*]

ModelSim evaluates the **find** command first and then sets variable *aluinputs* to the result of the find command. Obviously you don't want this type of behavior when specifying an array slice, so you would use curly brace escape characters:

add wave {/s/abc/data\_in[10:1]}

You must also use the escape characters if using VHDL syntax with spaces:

```

add wave {/s/abc/data_in(10 downto 1)}

```

### **Environment Variables and Pathnames**

You can substitute environment variables for pathnames in any argument that requires a pathname. For example:

vlog -v \$lib\_path/und1

Assuming you have defined \$lib\_path on your system, vlog will locate the source library file *und1* and search it for undefined modules. Refer to Environment Variables for more information.

# Name Case Sensitivity

Name case sensitivity is different for VHDL and Verilog. VHDL names are not case sensitive except for extended identifiers in VHDL 1076-1993 or later. In contrast, all Verilog names are case sensitive.

Names in ModelSim commands are case sensitive when matched against case sensitive identifiers, otherwise they are not case sensitive. SystemC names are case sensitive.

# **Extended Identifiers**

The following are supported formats for extended identifiers for any command that takes an identifier.

```

{\ext ident!\ }

# Note that trailing space before closing brace is required

\\ext\ ident\!\\

# All non-alpha characters escaped

```

# **Wildcard Characters**

You can use wildcard characters in HDL object names for the following simulator commands:

- add dataflow

- add list

- add memory

- add watch

- add wave

- find

- log

When you execute any of these commands with a wildcard, the default behavior is to exclude the following object types:

- VHDL shared variables in packages and design units, constants, generics, and immediate assertions

- Verilog parameters, specparams, memories

- PSL and SystemVerilog assertions, covers, and endpoints

- Signals in cells

You can alter these exclusions with the WildcardFilter preference variable. Refer to the section "Using the WildcardFilter Preference Variable" for more information.

Table 1-3 identifies thes supported wildcard characters.

| Character Syntax | Description                                                                                                                                                                 |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| *                | matches any sequence of characters                                                                                                                                          |

| ?                | matches any single character                                                                                                                                                |

| []               | matches any one of the enclosed<br>characters; a hyphen can be used to<br>specify a range (for example, a-z, A-Z,<br>0-9); can be used <i>only</i> with the find<br>command |

| Table 1-3. Wildcard Characters in HDL Object Names | Table 1-3 | . Wildcard | Characters | in HDL | Object Nam | es |

|----------------------------------------------------|-----------|------------|------------|--------|------------|----|

|----------------------------------------------------|-----------|------------|------------|--------|------------|----|

Note.

Note.

A wildcard character does not match a path separator. For example, /*dut*/\* will match /*dut/siga* and /*dut/clk*. However, /*dut*\* will not match either of those.

# **Using the WildcardFilter Preference Variable**

The WildcardFilter preference variable controls which object types are excluded when performing wildcard matches with simulator commands.

# -

Your WildcardFilter settings are persistent from one invocation to the next.

#### Procedure

#### Determining the Current WildcardFilter Variable Settings

Enter the following command:

#### set WildcardFilter

which returns a list of currently set arguments for exclusion.

#### Changing the WildcardFilter Settings from the Command Line

Refer to the list of WildcardFilter arguments in Table 1-4 to determine what you want to exclude from wildcard matches, then enter the following command:

#### set WildcardFilter "<argument> ..."

Note that you must enclose the space-separated list of arguments in quotation marks.

#### Changing the WildcardFilter Settings back to the Default

Enter the following command:

#### set WildcardFilter default

#### Changing the WildcardFilter settings from the GUI

- 1. Choose **Tools > Wildcard Filter** from the main menu.

- 2. Select the individual Filters you want to exclude from wildcard searches (Table 1-4 describes each option), or select Composite Filters to activate related filters (Table 1-5 describes each composite option).

- 3. Click OK.

#### WildcardFilter Argument Descriptions

Table 1-4 provides a list of the WildcardFilter arguments.

| Argument       | Description                                                                                                                                                                                                                                        |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Alias          | VHDL Alias                                                                                                                                                                                                                                         |

| Architecture   | VHDL Architecture                                                                                                                                                                                                                                  |

| Assertion      | Concurrent SystemVerilog or PSL assertion                                                                                                                                                                                                          |

| Block          | VHDL or Verilog block                                                                                                                                                                                                                              |

| CellInternal   | Signals in cells, where a cell is defined as 1) a module within a<br>'celldefine 2) a Verilog module found with a library search<br>(using either vlog -v or vlog -y) and compiled with vlog +libcell<br>or 3) a module containing a specify block |

| Class          | Verilog class declaration                                                                                                                                                                                                                          |

| ClassReference | SystemVerilog class reference                                                                                                                                                                                                                      |

| ClockingBlock  | Verilog clocking block                                                                                                                                                                                                                             |

| Compare        | Waveform comparison signal                                                                                                                                                                                                                         |

| Configuration  | Verilog configuration                                                                                                                                                                                                                              |

| Constant       | VHDL constant                                                                                                                                                                                                                                      |

| Cover          | SystemVerilog or PSL cover statements                                                                                                                                                                                                              |

| Covergroup     | SystemVerilog or PSL covergroup                                                                                                                                                                                                                    |

| Coverpoint     | Verilog coverpoint                                                                                                                                                                                                                                 |

| Cross          | Verilog cross                                                                                                                                                                                                                                      |

| Endpoint       | SystemVerilog assertion objects created for sequences on which<br>the method "ended/triggered" is used.<br>PSL assertion objects created for sequences for which the builtin<br>function "ended()" is used.                                        |

Table 1-4. WildcardFilter Arguments

| Argument        | Description                  |

|-----------------|------------------------------|

| Foreign         | VHDL foreign                 |

| Function        | Verilog function             |

| Generate        | VHDL generate                |

| Generic         | VHDL generic                 |

| ImmediateAssert | VHDL immediate assertions    |

| Integer         | VHDL integer                 |

| Interface       | SystemVerilog interface      |

| Memory          | Verilog memories             |

| Module          | Verilog module               |

| NamedEvent      | Verilog named event          |

| Net             | Verilog net                  |

| Package         | VHDL package                 |

| ParamClass      | Verilog parameterized class  |

| Parameter       | Verilog parameter            |

| Port            | Verilog port                 |

| Primitive       | Verilog primitive            |

| Process         | VHDL process                 |

| Property        | Assertion property           |

| Real            | Verilog real registers       |

| Reg             | Verilog register             |

| Root            | All objects                  |

| ScExport        | SystemC export               |

| ScHierChannel   | SystemC hierarchical channel |

| ScMethod        | SystemC method               |

| ScModule        | SystemC module               |

| ScPort          | SystemC port                 |

| ScPrimChannel   | SystemC primitive channel    |

| ScThread        | SystemC thread               |

| ScVariable      | SystemC variable             |

| Sequence        | SystemVerilog sequence       |

### Table 1-4. WildcardFilter Arguments

| Argument        | Description                                         |

|-----------------|-----------------------------------------------------|

| Signal          | VHDL signal                                         |

| SpecParam       | Verilog specparam                                   |

| Statement       | Verilog statement                                   |

| Task            | Verilog task                                        |

| TaThreadMon     | Assertion thread monitor object                     |

| Time            | Verilog time registers                              |

| TrStream        | Transaction stream                                  |

| TrStreamArray   | Transaction stream array                            |

| Variable        | VHDL shared variables in packages and design units. |

| VirtualExpr     | Virtual expression                                  |

| VirtualRegion   | Virtual region                                      |

| VirtualSignal   | Virtual signal                                      |

| vlGenerateBlock | Verilog generate block                              |

| vlPackage       | Verilog package                                     |

| vlProgram       | Verilog program                                     |

| vlTypedef       | Verilog typedef                                     |

#### Table 1-4. WildcardFilter Arguments

Table 1-5 provides a list of the group aliases of WildcardFilter arguments.

#### Table 1-5. WildcardFilter Argument Groups

| Group Argument   | Specific arguments included                                                                                                                                                                                                                                      |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AllVHDLScopes    | Architecture, Block, Generate, Package, Foreign                                                                                                                                                                                                                  |

| AllVHDL          | Architecture, Block, Generate, Package, Foreign, Process,<br>Signal, Variable, Constant, Generic, Alias                                                                                                                                                          |

| AllVerilogScopes | Block, vlGenerateBlock, Module, Task, Function,<br>Statement, Class, Cross, Covergroup, Coverpoint,<br>vlPackage, vlTypedef, ParamClass, ClockingBlock                                                                                                           |

| AllVerilogVars   | Parameter, Reg, Integer, Time, Real, SpecParam, Memory,<br>NamedEvent, ClassReference                                                                                                                                                                            |

| AllVerilog       | Block, vlGenerateBlock, Module, Primitive, Task,<br>Function, Statement, Net, Parameter, Reg, Integer, Time,<br>Real, SpecParam, Memory, NamedEvent, Class, Cross,<br>Covergroup, Coverpoint, vlPackage, vlTypedef,<br>ParamClass, ClockingBlock, ClassReference |

| Group Argument    | Specific arguments included                                                                                                                                                                                                                                                                                                                         |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VirtualSignals    | VirtualSignal, VirtualExpr                                                                                                                                                                                                                                                                                                                          |

| Virtual           | VirtualRegion, VirtualSignal, VirtualExpr                                                                                                                                                                                                                                                                                                           |

| SystemCSignals    | ScPrimChannel, ScPort, ScExport                                                                                                                                                                                                                                                                                                                     |

| SystemCProcess    | ScMethod, ScThread                                                                                                                                                                                                                                                                                                                                  |

| SystemC           | ScModule, ScPrimChannel, ScVariable, ScPort,<br>ScMethod, ScThread, ScExport, ScHierChannel                                                                                                                                                                                                                                                         |

| TR                | TrStream, TrStreamArray                                                                                                                                                                                                                                                                                                                             |

| AllHDLScopes      | Architecture, Block, Generate, Package, Foreign,<br>vlGenerateBlock, Module, Task, Function, Statement,<br>Class, Cross, Covergroup, Coverpoint, vlPackage,<br>vlTypedef, ParamClass, ClockingBlock                                                                                                                                                 |

| AllHDLSignals     | Signal, Variable, Constant, Generic, Alias, Net, Parameter,<br>Reg, Integer, Time, Real, SpecParam, Memory,<br>NamedEvent, VirtualSignal, VirtualExpr, ClassReference                                                                                                                                                                               |

| AllVariables      | Variable, Constant, Generic, Alias, Parameter, Reg,<br>Integer, Time, Real, SpecParam, Memory, NamedEvent,<br>ClassReference                                                                                                                                                                                                                        |

| AllHDLSignalsVars | Signal, Variable, Constant, Generic, Alias, Net, Parameter,<br>Reg, Integer, Time, Real, SpecParam, Memory,<br>NamedEvent, VirtualSignal, VirtualExpr, ClassReference                                                                                                                                                                               |

| AllHDL            | Architecture, Block, Generate, Package, Foreign,<br>vlGenerateBlock, Signal, Variable, Module, Task,<br>Function, Statement, Net, Parameter, Reg, Integer, Time,<br>Real, SpecParam, Memory, NamedEvent, VirtualSignal,<br>VirtualExpr, Class, Cross, Covergroup, Coverpoint,<br>vlPackage, vlTypedef, ParamClass, ClockingBlock,<br>ClassReference |

| AllScopes         | Architecture, Block, Generate, Package, Foreign,<br>vlGenerateBlock, Module, Task, Function, Statement,<br>VirtualRegion, ScModule, Class, Cross, Covergroup,<br>Coverpoint, vlPackage, vlTypedef, ParamClass,<br>ClockingBlock                                                                                                                     |

| AllSignals        | Signal, Net, Parameter, Reg, Integer, Time, Real,<br>SpecParam, Memory, NamedEvent, VirtualSignal,<br>VirtualExpr, ScPrimChannel, Endpoint, ScPort, TrStream,<br>TrStreamArray, ScExport, ClassReference                                                                                                                                            |

Table 1-5. WildcardFilter Argument Groups

| Group Argument | Specific arguments included                                                                                                                                                                                                                                 |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AllSignalsVars | Signal, Variable, Constant, Generic, Alias, Net, Parameter,<br>Reg, Integer, Time, Real, SpecParam, Memory,<br>NamedEvent, VirtualSignal, VirtualExpr, ScPrimChannel,<br>Endpoint, ScVariable, ScPort, TrStream, TrStreamArray,<br>ScExport, ClassReference |

| AllConstants   | Constant, Generic, Parameter, SpecParam                                                                                                                                                                                                                     |

| AllProcesses   | Process, ScMethod, ScThread                                                                                                                                                                                                                                 |

| Default        | Variable, Constant, Generic, Parameter, SpecParam,<br>Memory, Assertion, Cover, Endpoint, ScVariable,<br>CellInternal, ImmediateAssert                                                                                                                      |

# **Simulator Variables**

ModelSim variables can be referenced in simulator commands by preceding the name of the variable with the dollar sign (\$) character. ModelSim uses global variables for simulator state variables, simulator control variables, simulator preference variables, and user-defined variables. Refer to modelsim.ini Variables in the User's Manual for more information on variables.

The report command returns a list of current settings for either the simulator state or simulator control variables.

# **Simulation Time Units**

You can specify the time unit for delays in all simulator commands that have time arguments. For example:

```

force clk 1 50 ns, 1 100 ns -repeat 1 us run 2 ms \,

```

Note that all the time units in a ModelSim command need not be the same.

Unless you specify otherwise as in the examples above, simulation time is always expressed using the resolution units that are specified by the UserTimeUnit variable.

By default, the specified time units are assumed to be relative to the current time unless the value is preceded by the character @, which signifies an absolute time specification.

# **Argument Files**

You can load additional arguments into some commands by using argument files, which are specified with the -f argument. The following commands support the -f argument:

sccom vlog vcom vencrypt vmake vopt vsim

The **-f <filename>** argument specifies a file that contains additional command line arguments. The following sections outline some syntax rules for argument files.

• Single Quotes ( ' ' )— allows you to group arbitrary characters so that no character substitution occurs within the quotes, such as environment variable expansion or escaped characters.

```

+acc=rn+'\mymodule' //does not treat the '\' as an escape character

```

• Double Quotes ( " " )— allows you to group arbitrary characters so that Tcl-style backslash substitution and environment variable expansion is performed.

```

+acc=rn+"\\mymodule\\$VAR"

// escapes the path separators (\) and substitues

// your value of `$VAR'

```

- Unquoted the following are notes on what occurs when some information is not quoted:

- $\circ~$  Tcl backslash substitution any unquoted backslash (  $\backslash$  ) will be treated as an escape character.

```

+acc=rn\\mymodule

// the leading '\' is considered an escape character

```

Environment variable expansion — any unquoted environment variable, such as \$envname, will be expanded. You can also use curly braces ({}) in your environment variable, such as \${envname}.

```

+acc=rn\\$MODULE

// the leading '\' is considered an escape character and the

// variable $MODULE is expanded

```

- Newline Character you can specify arguments on separate lines in the argument file, with the newline characters treated as space characters. There is no need to put a backslash (\) at the end of each line.

- Comments Comments within the argument files follow these rules:

- All text in a line beginning with // to its end is treated as a comment.

- $\circ~$  All text bracketed by /\* ... \*/ is treated as a comment.

# **Command Shortcuts**

- You may abbreviate command syntax, but there's a catch the minimum number of characters required to execute a command are those that make it unique. Remember, as we add new commands some of the old shortcuts may not work. For this reason ModelSim does not allow command name abbreviations in macro files. This minimizes your need to update macro files as new commands are added.

- Multiple commands may be entered on one line if they are separated by semi-colons (;). For example:

#### ModelSim> vlog -nodebug=ports level3.v level2.v ; vlog -nodebug top.v

The return value of the last function executed is the only one printed to the transcript. This may cause some unexpected behavior in certain circumstances. Consider this example:

#### vsim -c -do "run 20 ; simstats ; quit -f" top

You probably expect the **simstats** results to display in the Transcript window, but they will not, because the last command is **quit -f**. To see the return values of intermediate commands, you must explicitly print the results. For example:

```

vsim -do "run 20 ; echo [simstats]; quit -f" -c top

```

# **Command History Shortcuts**

You can review simulator command history or rerun previous commands by using keyboard shortcuts at the ModelSim/VSIM prompt. Table 1-6 contains a list of these shortcuts.

| Shortcut           | Description                                                                                                                                 |

|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| !!                 | repeats the last command                                                                                                                    |

| !n                 | repeats command number n; n is the VSIM prompt<br>number (e.g., for this prompt: VSIM 12>, n =12)                                           |

| !abc               | repeats the most recent command starting with "abc"                                                                                         |

| ^xyz^ab^           | replaces "xyz" in the last command with "ab"                                                                                                |

| up and down arrows | scrolls through the command history with the keyboard arrows                                                                                |

| click on prompt    | left-click once on a previous ModelSim or VSIM<br>prompt in the transcript to copy the command typed at<br>that prompt to the active cursor |

| his or history     | shows the last few commands (up to 50 are kept)                                                                                             |

Table 1-6. Keyboard Shortcuts for Command History

# **Numbering Conventions**

Numbers in ModelSim can be expressed in either VHDL or Verilog style. You can use two styles for VHDL numbers and one for Verilog.

# **VHDL Numbering Conventions**

There are two types of VHDL number styles:

### **VHDL Style 1**

[ - ] [ radix # ] value [ # ]

| Element | Description                                                                                                                       |  |

|---------|-----------------------------------------------------------------------------------------------------------------------------------|--|

| -       | indicates a negative number; optional                                                                                             |  |

| radix   | can be any base in the range 2 through 16 (2, 8, 10, or 16); by default, numbers are assumed to be decimal; optional              |  |

| value   | specifies the numeric value, expressed in the specified radix; required                                                           |  |

| #       | is a delimiter between the radix and the value; the first # sign is required<br>if a radix is used, the second is always optional |  |

#### Table 1-7. VHDL Number Conventions: Style 1

A '-' can also be used to designate a "don't care" element when you search for a signal value or expression in the List or Wave window. If you want the '-' to be read as a "don't care" element, rather than a negative sign, be sure to enclose the number in double quotes. For instance, you would type "-0110--" as opposed to -0110--. If you don't include the double quotes, ModelSim will read the '-' as a negative sign. For example:

16#FFca23# 2#11111110 -23749

### VHDL Style 2

base "value"

| Element | Description                                                                                                |  |

|---------|------------------------------------------------------------------------------------------------------------|--|

| base    | specifies the base; binary: B, octal: O, hex: X; required                                                  |  |

| "value" | specifies digits in the appropriate base with optional underscore separators; default is decimal; required |  |

Table 1-8. VHDL Number Conventions: Style 2

For example:

B"11111110" X"FFca23"

### Searching for VHDL Arrays in the Wave and List Windows

Searching for signal values in the Wave or List window may not work correctly for VHDL arrays if the target value is in decimal notation. You may get an error that the value is of incompatible type. Since VHDL does not have a radix indicator for decimal, the target value may get misinterpreted as a scalar value. Prefixing the value with the Verilog notation 'd should eliminate the problem, even if the signal is VHDL.

# **Verilog Numbering Conventions**

Verilog numbers are expressed in the style:

[ - ] [ size ] [ base ] value

| Element | Description                                                                                                |  |

|---------|------------------------------------------------------------------------------------------------------------|--|

| -       | indicates a negative number; optional                                                                      |  |

| size    | the number of bits in the number; optional                                                                 |  |

| base    | specifies the base; binary: 'b or 'B, octal: 'o or 'O, decimal: 'd or 'D, hex: 'h or 'H; optional          |  |

| value   | specifies digits in the appropriate base with optional underscore separators; default is decimal; required |  |

#### Table 1-9. Verilog Number Conventions

A '-' can also be used to designate a "don't care" element when you search for a signal value or expression in the List or Wave windows. If you want the '-' to be read as a "don't care" element, rather than a negative sign, be sure to enclose the number in double quotes. For instance, you would type "-0110--" as opposed to 7'b-0110--. If you don't include the double quotes, ModelSim will read the '-' as a negative sign. For example:

| 8′b11111110 |

|-------------|

| 21'Hlfca23  |

|             |

|             |

# **GUI\_expression\_format**

The GUI\_expression\_format is an option of several simulator commands that operate within the ModelSim GUI environment. The expressions help you locate and examine objects within the List and Wave windows (expressions may also be used through the **Edit > Search** menu in both windows). The commands that use the expression format are:

compare add, compare clock, compare configure, configure, examine, searchlog, virtual function, virtual signal, down, left, right, up.

# **Expression Typing**

GUI expressions are typed. The supported types consist of the following scalar and array types.

### **Scalar Types**

The scalar types are as follows: boolean, integer, real, time (64-bit integer), enumeration, and signal state. Signal states are represented by the nine VHDL std\_logic states: 'U' 'X' '0' '1' 'Z' 'W' 'L' 'H' and '-'.

Verilog states 0, 1, x, and z are mapped into these states and the Verilog strengths are ignored. Conversion is done automatically when referencing Verilog nets or registers.

SystemC scalar types supported are: all the C/C++ types except class, structure, union, and array, as well as SystemC types sc\_logic and sc\_bit.

### **Array Types**

The supported array types are signed and unsigned arrays of signal states. This would correspond to the VHDL std\_logic\_array type. Verilog registers are automatically converted to these array types. The array type can be treated as either UNSIGNED or SIGNED, as in the IEEE std\_logic\_arith package. Normally, referencing a signal array causes it to be treated as UNSIGNED by the expression evaluator; to cause it to be treated as SIGNED, use casting as described below. Numeric operations supported on arrays are performed by the expression evaluator via ModelSim's built-in numeric\_standard (and similar) package routines. The expression evaluator selects the appropriate numeric routine based on SIGNED or UNSIGNED properties of the array arguments and the result.

The enumeration types supported are any VHDL enumerated type. Enumeration literals may be used in the expression as long as some variable of that enumeration type is referenced in the expression. This is useful for sub-expressions of the form:

```

(/memory/state == reading)

```

The supported SystemC aggregate types are the C/C++ array types: union, class, structure, and array. Also supported are the SystemC array types:  $sc_bv < w >$ ,  $sc_lv < w >$ ,  $sc_int < w >$ , etc.

# **Expression Syntax**

GUI expressions generally follow C-language syntax, with both VHDL-specific and Verilogspecific conventions supported. These expressions are not parsed by the Tcl parser, and so do not support general Tcl; parentheses should be used rather than braces. Procedure calls are not supported. A GUI expression can include the following elements: Tcl macros, constants, array constants, variables, array variables, signal attributes, operators, and casting.

### **Tcl Macros**

Macros are useful for pre-defined constants or for entire expressions that have been previously saved. The substitution is done only once, when the expression is first parsed. Macro syntax is:

\$<name>

Substitutes the string value of the Tcl global variable <name>.

### Constants

| Туре                 | Values                                                                                                                               |  |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------------|--|

| boolean value        | true false TRUE FALSE                                                                                                                |  |

| integer              | [0-9]+                                                                                                                               |  |

| real number          | $\langle int \rangle   ([\langle int \rangle], \langle int \rangle [exp]) \rangle$ where the optional $[exp]$ is: $(e E)[+ -][0-9]+$ |  |

| time                 | integer or real optionally followed by time unit                                                                                     |  |

| enumeration          | VHDL user-defined enumeration literal                                                                                                |  |